However, such caches generally do not perform well for random access patterns as there will be high number of misses in the address lookup process.

To mitigate the impact of address redirection in wear leveling, certain conventional acceleration mechanisms, such as caching of each level of the lookup structure, are commonly employed, with the caches generally being resident in the NVM Controller.

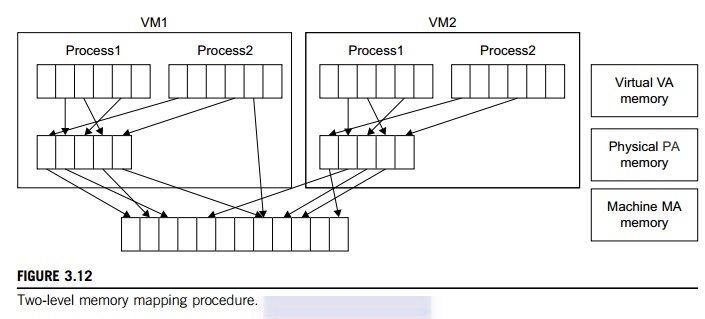

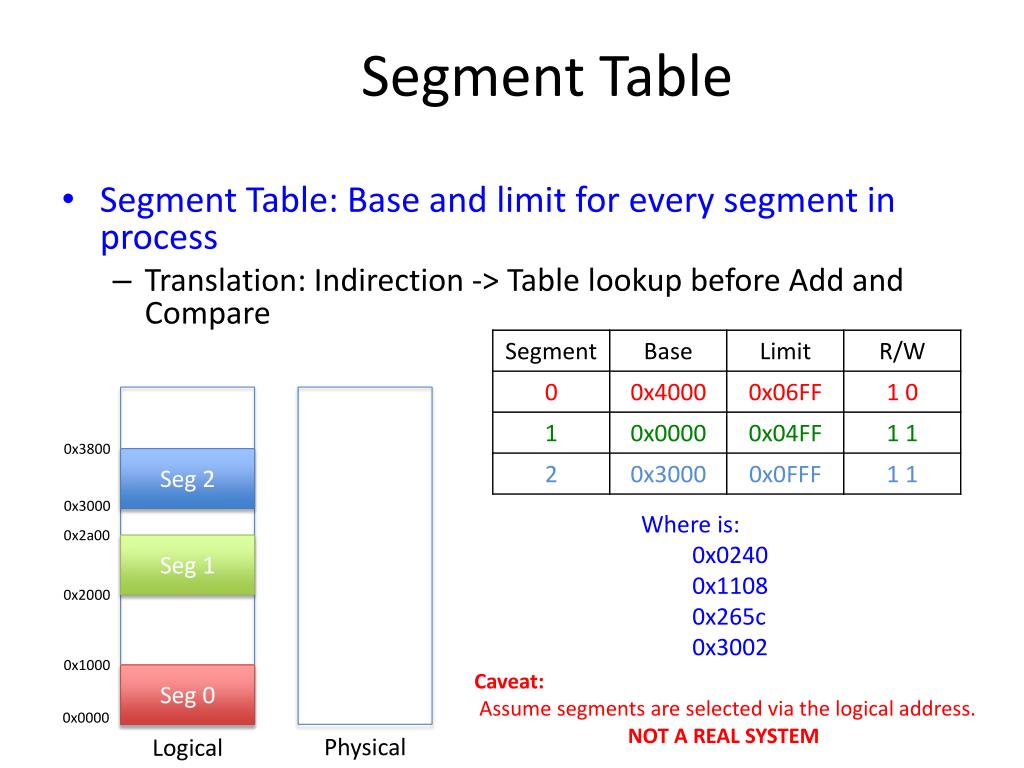

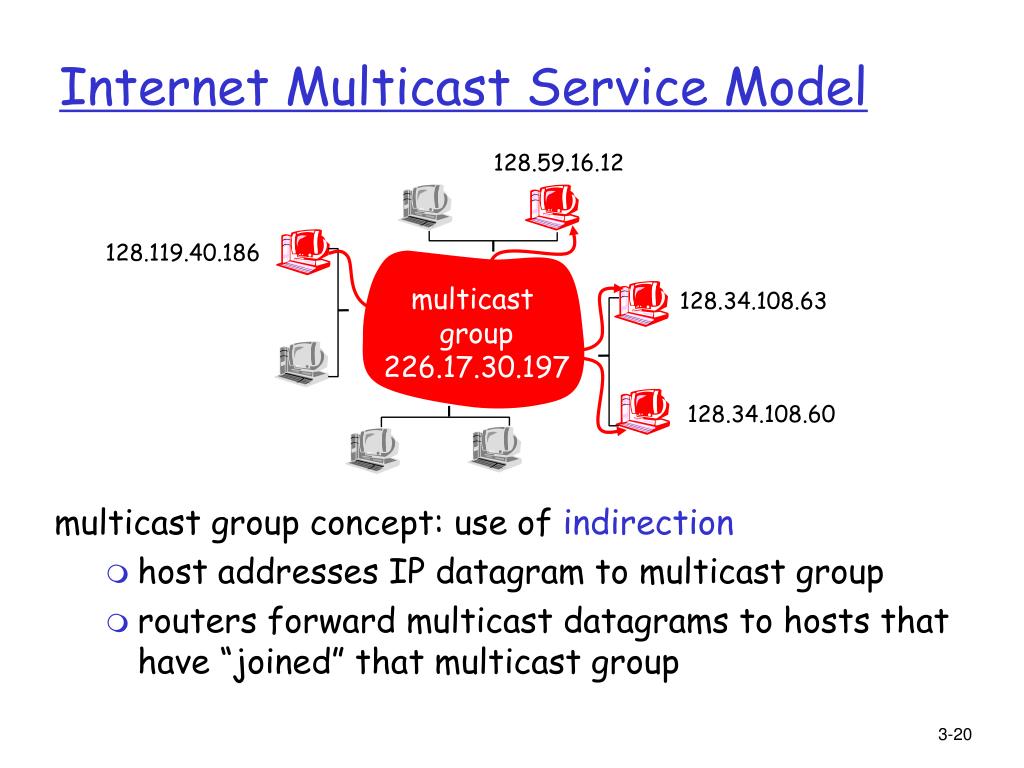

For this reason, the AIT presents a multi-level look-up structure that has very high performance cost. Such large tables generally need to reside in the NVM itself, and thus need to be wear-leveled as well to maximize the lifespan of the memory. However, Address Indirection Tables (AIT) for nonvolatile memory can be very large depending on the size of the NVM as well as the size of the wear-level block. Re-directing writes implies an address indirection mechanism that can re-map CPU generated memory address (System Address) to an NVM Address that can be re-located based on the wear-leveling algorithm. Wear-leveling involves re-directing writes from one physical NVM block to another in order to ensure uniform wearing of all blocks. Nonvolatile memory (NVM) based memory systems utilize wear-leveling in order to extend the write endurance of the memory, where nonvolatile memory generally has a limited number erase cycles before the memory is no longer reliable. Nonvolatile memory includes, but is not limited to, flash memory (including NAND flash memory, such as included in non-volatile memory chips, and NOR flash memory), and other suitable non-volatile memory such as phase change memory (PCM), a byte addressable three dimensional cross point memory, a resistive memory, nanowire memory, ferro-electric transistor random access memory (FeTRAM), magnetoresistive random access memory (MRAM) memory that incorporates memristor technology, spin transfer torque (STT)-MRAM, and byte addressable random access non-volatile memory. “Nonvolatile memory” means memory that retains a stored value without connection to a power source. Volatile memory includes RAM, such as DRAM. “Volatile memory” means memory that does not retain a stored value without connection to a power source. Main memory is commonly random access memory (RAM), and specifically is commonly dynamic random access memory (DRAM). “Main memory”, “primary memory”, or “system memory” is computer memory that a processor or computer primarily accesses for programs and data. 7 is an illustration of an embodiment of an electronic apparatus or system including accelerated lookup for nonvolatile memory.DETAILED DESCRIPTIONĮmbodiments described herein are generally directed to accelerated address indirection table lookup for wear-leveled non-volatile memory. 6 is a flowchart to illustrate a process for nonvolatile memory lookup according to an embodiment andįIG. 5 is a diagram to illustrate a nonvolatile memory module according to embodiment įIG. 4 is an illustration of an accelerated lookup for a nonvolatile memory according to an embodiment įIG. 3 is an illustration of an address lookup for a nonvolatile memory including caching įIG. 2 is an illustration of an example of an address indirection table structure įIG. 1 is an illustration of nonvolatile memory with shadow table access to provide accelerated address indirection, according to an embodiment įIG. Large tables generally are required reside in the non-volatile memory itself, and thus need to be wear-leveled as well, causing the AIT to be a multi-level look-up structure with a high performance cost.BRIEF DESCRIPTION OF THE DRAWINGSĮmbodiments described here are illustrated by way of example, and not by way of limitation, in the figures of the accompanying drawings in which like reference numerals refer to similar elements.įIG. However, AITs can be very large depending on the size of the non-volatile memory, as well as the size of the wear-level block. Because of the wear caused to non-volatile memory by writing actions, the NVM based memory systems use wear-leveling in order to maximize write endurance.įurther, data is commonly mapped to different locations in the memory using address re-directing, wherein the system addresses and non-volatile memory addresses are translated in a table, commonly referred to as an Address Indirection Table (AIT). Embodiments described herein generally relate to the field of electronic devices and, more particularly, to accelerated address indirection table lookup for wear-leveled non-volatile memory.Ĭomputer operations include the use of non-volatile memory (NVM) to maintain certain data.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed